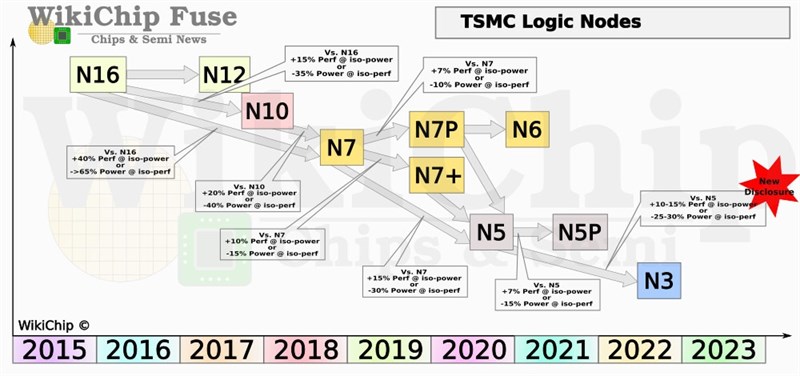

TSMC vừa công bố chi tiết về quy trình sản xuất chip 3nm mới, đạt tới 250 triệu transistor/mm²

Hôm nay, nhà sản xuất chip di động TSMC đã chính thức công bố chi tiết về quy trình sản xuất chip 3nm mới nhất của mình. Mật độ bóng bán dẫn (transistor) của quy trình này tạo ra một kỷ lục mới, 250 triệu transistor/mm².

Để tiện so sánh, chip Kirin 990 5G với quy trình EUV 7nm có kích thước 113.31 mm², số bóng bán dẫn là 10.3 tỷ, trung bình đạt 90 triệu transistor/mm². Như vậy, mật độ bóng bán dẫn của chip 3nm gấp gần 3 lần so với quy trình 7nm.

Về hiệu suất, chip TSMC 5nm có hiệu suất cao hơn 10% – 15% so với chip 7nm và mức tiêu thụ năng lượng giảm 25% – 30%. Tuy nhiên, hiệu suất 3nm cao hơn 5% so với 5nm và mức tiêu thụ năng lượng giảm thêm 15%.

Về mật độ transistors, TSMC cho biết chip 3nm có mật độ transistors tăng 1.7 lần so với quy trình 5nm. Cũng theo WikiChip, chip 3nm nên cung cấp mật độ transistors ở mức dưới 300 triệu bóng bán dẫn trên mỗi milimet vuông.

Chưa hết, TSMC chia sẻ thêm rằng, việc phát triển quy trình 3nm phù hợp với lịch trình ban đầu mà hãng đã công bố. Theo Giám đốc điều hành của TSMC, ông CC Wei, TSMC sẽ bắt đầu sản xuất thử nghiệm chip 3nm vào năm 2021. Việc sản xuất hàng loạt sẽ bắt đầu vào nửa cuối năm 2022.

Xem thêm: Qualcomm nói gì khi bị MediaTek cáo buộc cũng gian lận điểm hiệu năng?

Về công nghệ, TSMC đã đánh giá các lựa chọn khác nhau và tin rằng quy trình FinFET hiện tại tốt hơn về chi phí và hiệu quả năng lượng. Do đó, chip 3nm đầu tiên vẫn sẽ sử dụng công nghệ bóng bán dẫn FinFET.

Dẫu vậy, đối thủ của TSMC là Samsung đang đặt cược vào chip 3nm để có thể vượt mặt TSMC trên thị trường chip di động. Do đó, sự tiến bộ và lựa chọn công nghệ của Samsung là rất triệt để. Samsung đã phát triển quy trình 3nm dựa trên công nghệ GAAFET (Gate All Quanh Trans-Field Transitor), một bước kế thừa của công nghệ FinFET hiện nay.

Bạn có đang mong chờ smartphone dùng chip 3nm không? Nhớ like và share để ủng hộ mình nhé!

(Nguồn: Gizchina)